# **Stratix 10 High-Performance Design Handbook**

S10HPHB 2016.08.07

# **Contents**

| 1 Int | roduction                                                      | . 4 |

|-------|----------------------------------------------------------------|-----|

|       | 1.1 HyperFlex Architecture Overview                            | 4   |

|       | 1.1.1 Hyper-Aware Design Flow                                  |     |

|       | 1.2 Acknowledgments                                            |     |

| 2 RTI | L Design Guidelines                                            | . 9 |

|       | 2.1 HyperFlex Design Philosophy                                |     |

|       | 2.1.1 Set a High-Speed Target                                  |     |

|       | 2.1.2 Experiment and Iterate                                   |     |

|       | 2.1.3 Compile Components Independently                         |     |

|       | 2.1.4 Optimize Sub-Modules                                     |     |

|       | 2.1.5 Avoid Broadcast Signals                                  |     |

|       | 2.2 Facilitate Register Movement (Hyper-Retiming)              |     |

|       | 2.2.1 Reset Strategies                                         |     |

|       | 2.2.2 Clock Enable Strategies                                  |     |

|       | 2.2.3 Synthesis Attributes                                     |     |

|       | 2.2.4 Timing Constraint Considerations                         |     |

|       | 2.2.5 Clock Synchronization Strategies                         |     |

|       | 2.2.6 Synchronizers                                            |     |

|       | 2.3 Add Pipeline Registers (Hyper-Pipelining)                  | 26  |

|       | 2.3.1 Conventional versus Hyper-Pipelining                     |     |

|       | 2.3.2 Pipelining and Latency                                   | 27  |

|       | 2.3.3 Use Registers Instead of Multicycle Exceptions           | 28  |

|       | 2.4 Optimize RTL (Hyper-Optimization)                          | 28  |

|       | 2.4.1 Deciding When to Rewrite the RTL                         |     |

|       | 2.4.2 General Optimization Techniques                          |     |

|       | 2.4.3 Specific Design Structures                               |     |

|       | 2.5 Appendix: Parameterizable Pipeline Modules                 | 50  |

| 3 Rui | nning the Quartus Prime Pro – Stratix 10 Edition Beta Software | 53  |

|       | 3.1 System Requirements                                        | .53 |

|       | 3.1.1 Licensing                                                | 54  |

|       | 3.2 Recommended Design Flow                                    |     |

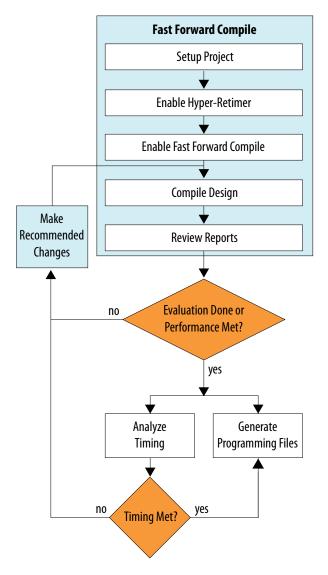

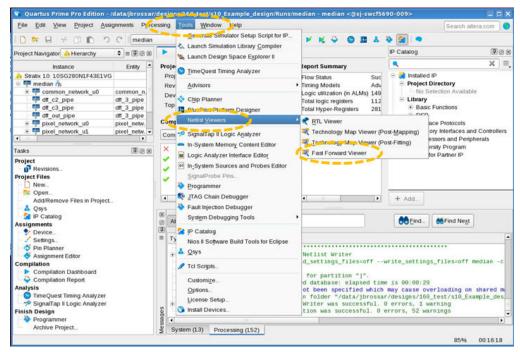

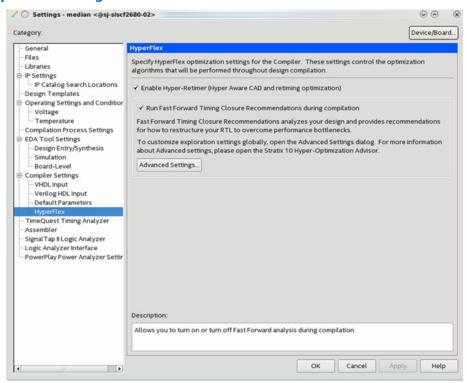

|       | 3.2.1 Step 1: Enable and Run Fast Forward Compile              | 56  |

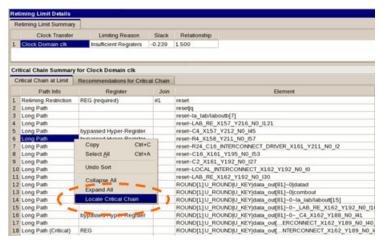

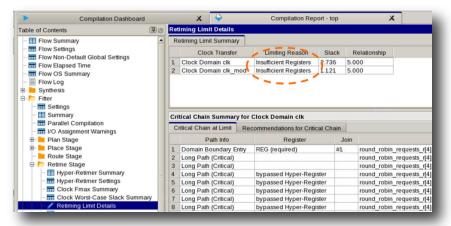

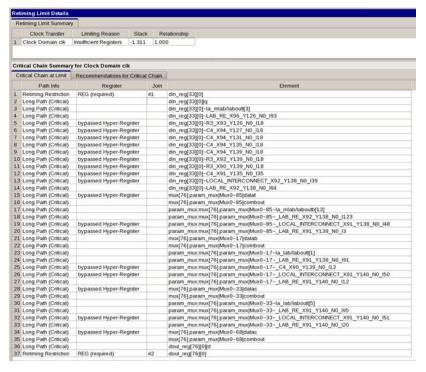

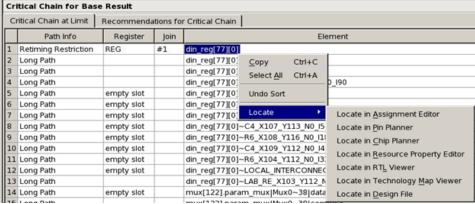

|       | 3.2.2 Step 2: Review Critical Chain Reports                    | 57  |

|       | 3.2.3 Step 3: Implement Performance Recommendations            | 58  |

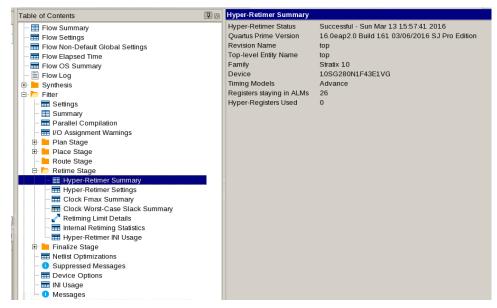

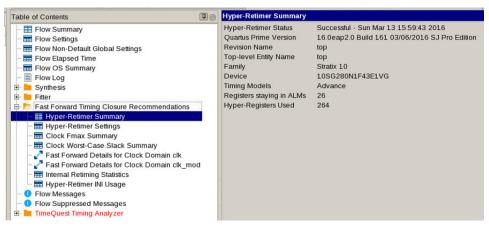

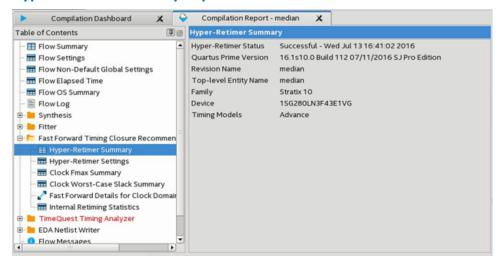

|       | 3.3 Using the Hyper-Retimer                                    |     |

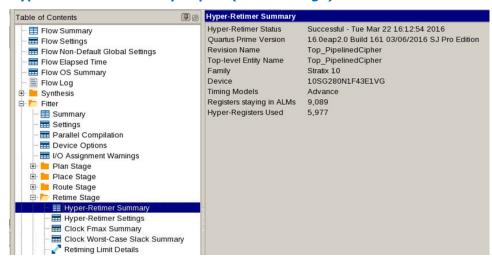

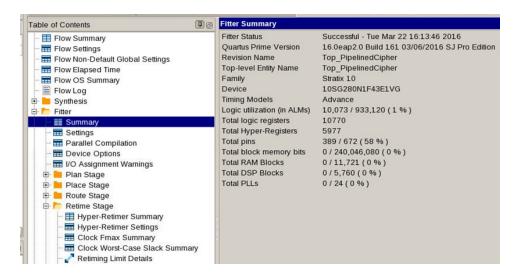

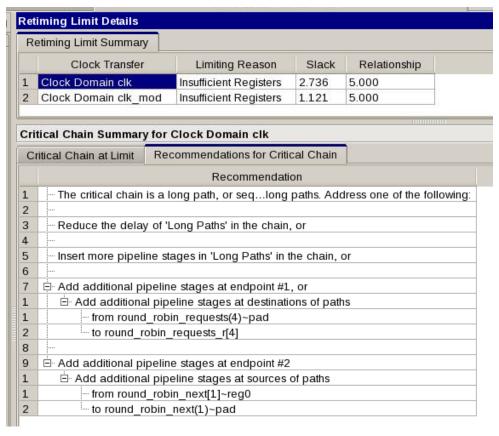

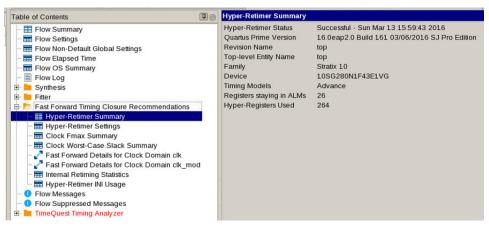

|       | 3.3.1 Interpreting Hyper-Retimer Reports                       |     |

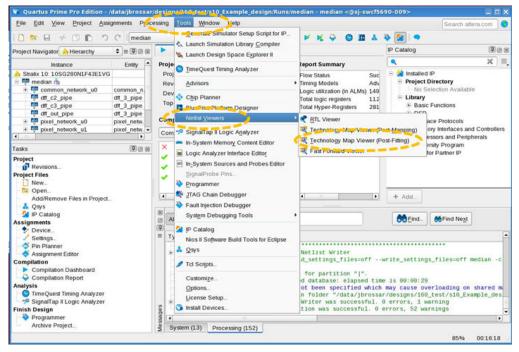

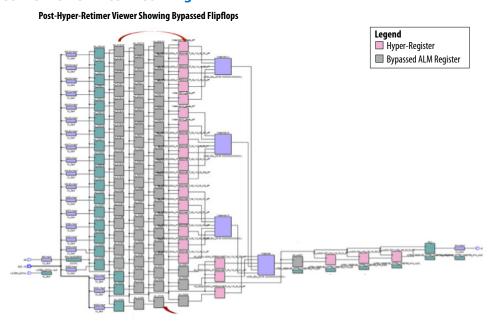

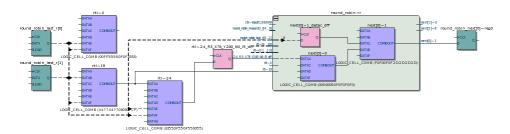

|       | 3.3.2 Viewing the Hyper-Retimer Netlist                        | 62  |

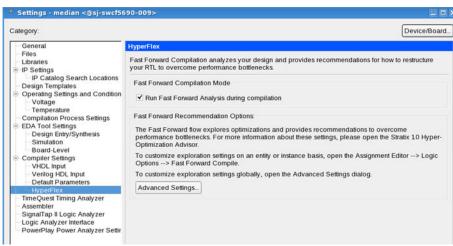

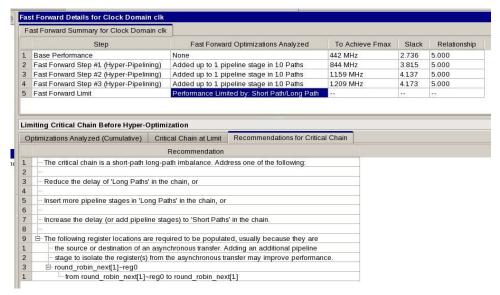

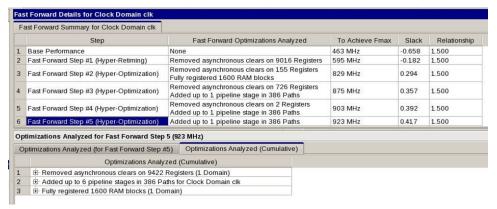

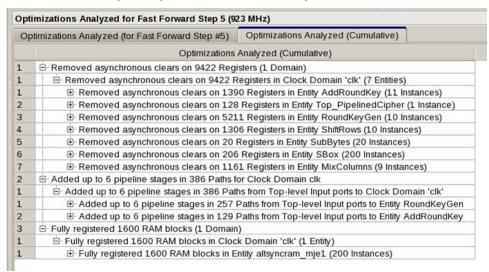

|       | 3.4 Using Fast Forward Compilation                             |     |

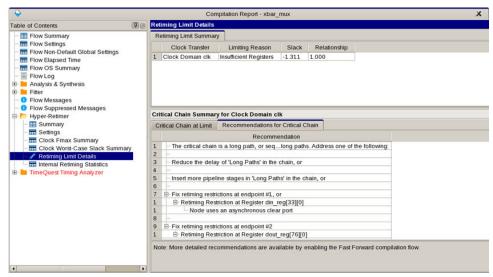

|       | 3.4.1 Interpreting Fast Forward Compile Reports                |     |

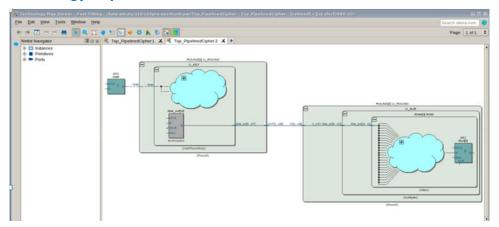

|       | 3.4.2 Viewing the Fast Forward Compile Netlist                 |     |

|       | 3.5 Interpreting Critical Chain Reports                        |     |

|       | 3.5.1 Types of Critical Chains                                 |     |

|       | 3.5.2 Details about Critical Chain Reports                     |     |

|       | 3.6 Retiming Restrictions and Workarounds                      | ٩n  |

### Contents

| 4 HyperFlex Porting Guidelines                                       | 92  |

|----------------------------------------------------------------------|-----|

| 4.1 Suggested Scope for Performance Exploration and Design Migration | 92  |

| 4.1.1 Black-boxing Verilog HDL Modules                               |     |

| 4.1.2 Black-boxing VHDL Modules                                      | 94  |

| 4.1.3 Clock Management                                               | 96  |

| 4.1.4 Pin Assignments                                                | 96  |

| 4.1.5 Transceiver Control Logic                                      | 97  |

| 4.1.6 Upgrade Outdated IP Cores                                      | 98  |

| 4.2 Top-Level Design Considerations                                  | 98  |

| 4.3 Summary                                                          | 99  |

| 5 Design Example Walk-Through                                        | 100 |

| 5.1 Median Filter Design Example                                     |     |

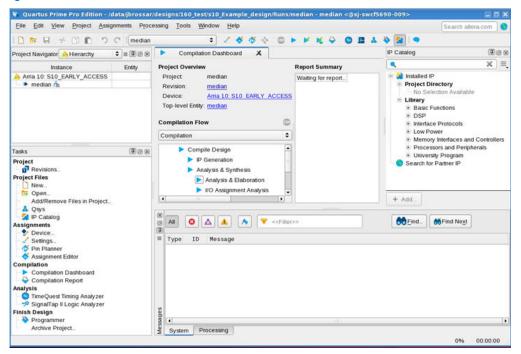

| 5.1.1 Step 1: Setup the Project                                      |     |

| 5.1.2 Step 2: Run Fast-Forward Compilation                           |     |

| 5.1.3 Step 3: View Fast-Forward Recommendations                      |     |

| 5.1.4 Step 4: Implement Fast-Forward Recommendations                 |     |

| 6 Optimization Example                                               | 111 |

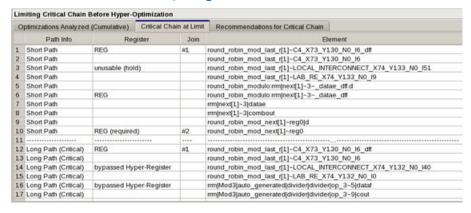

| 6.1 Round Robin Scheduler                                            |     |

| 7 Glossary                                                           |     |

| 8 Document Revision History                                          | 118 |

| A Appendix: Clock Enables and Resets                                 | 119 |

| A.1 Synchronous Resets and Limitations                               | 119 |

| A.1.1 Synchronous Resets Summary                                     | 121 |

| A.2 Retiming with Clock Enables                                      | 123 |

| A.2.1 Example for Broadcast Control Signals                          | 125 |

| A.3 Resolving Short Paths                                            | 127 |

## 1 Introduction

This document describes design techniques for achieving the highest performance with the  $Stratix^{\$}$  10 HyperFlex $^{\$}$  device architecture. The Stratix 10 architecture introduces new Hyper-Retiming, Hyper-Pipelining, and Hyper-Optimization design techniques for Intel FPGAs. Use these techniques to reach the highest clock frequencies in Stratix 10 devices.

- HyperFlex architecture overview—introduces the new Stratix 10 device architecture and supporting software features

- RTL design guidelines—provides fundamental high-performance RTL design techniques forStratix 10 designs

- Running Quartus® Prime Pro Stratix 10 Edition Beta software—describes compiling for Stratix 10 devices and performance optimization features

- HyperFlex porting guidelines—design preparations to compile and optimize for Stratix 10 devices

- Design example walk-through—steps through the provided median filter Stratix 10design, analyzes the results, and demonstrates performance improvement techniques

## 1.1 HyperFlex Architecture Overview

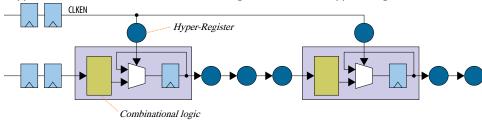

The centerpiece of the Stratix 10 HyperFlex architecture is the innovative "registers everywhere" design. This architecture adds bypassable Hyper-Registers to every routing segment in the Stratix 10 device core, and at all functional block inputs.

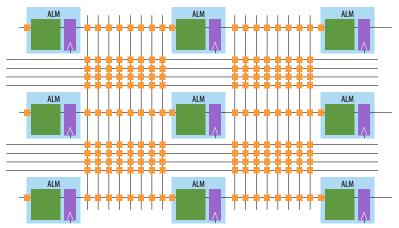

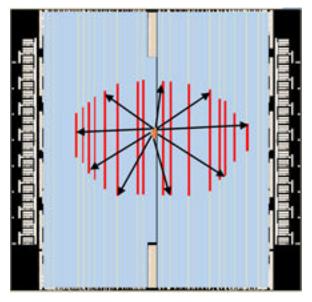

Figure 1. Registers Everywhere - HyperFlex Architecture

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2008 Registered

The Registers Everywhere illustration shows a small section of the Intel FPGA fabric, with nine ALMs and the interconnect routing that connects the ALMs. The squares at the intersection of each horizontal and vertical routing segment indicate the Hyper-Register location.

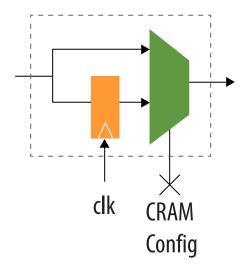

## Figure 2. Bypassable Hyper-Register

The routing signal can bypass the register and go straight to the multiplexer, or go through the register first. One bit of the Intel FPGA configuration memory (CRAM) controls this multiplexer.

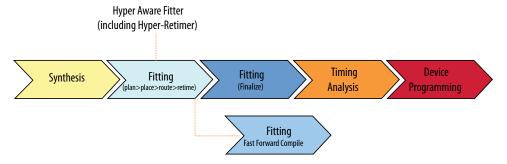

## 1.1.1 Hyper-Aware Design Flow

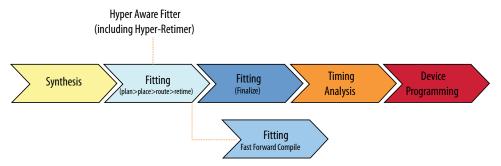

The Quartus Prime Pro – Stratix 10 Edition Beta software introduces a powerful suite of integrated capabilities to take full advantage of the HyperFlex architecture and maximize design productivity.

The Hyper-Aware Design Flow automatically optimizes designs to take advantage of the HyperFlex architecture. The Fitter anticipates the fine-grained Hyper-Retiming optimizations that occur in the subsequent retime stage of the Fitter. Therefore, you can focus the earlier stages of optimization on critical paths that do not benefit as much from retiming.

To improve design performance, enable more retiming optimizations by removing retiming restrictions (Hyper-Retiming), adding pipeline stages (Hyper-Pipelining) or modifying the structure of the design (Hyper-Optimization).

Figure 3. Hyper-Aware Design Flow

The Hyper-Registers allow you to use familiar design techniques to increase the performance of the design beyond other conventional FPGA architectures. As FPGA process geometries shrink, the interconnect delays between the ALMs become dominant and limit performance. Locating the Hyper-Registers in the interconnect routing—where they can best address this issue—is one of the key innovations of the HyperFlex architecture. When implementing these techniques in Hyper-Registers, rather than ALMs, the techniques are known as Hyper-Retiming, Hyper-Pipelining, and Hyper-Optimization.

Use this three-step process to maximize the performance of a design for the HyperFlex architecture:

Table 1. Three Steps to Maximize HyperFlex Architecture Performance

| Step | Architecture Advantage | Required Changes           | Core Performance (versus previous-<br>generation high-performance Intel<br>FPGA) |

|------|------------------------|----------------------------|----------------------------------------------------------------------------------|

| 1    | Hyper-Retiming         | None, or minor RTL changes | 1.4X                                                                             |

| 2    | Hyper-Pipelining       | Added pipelining           | 1.6X                                                                             |

| 3    | Hyper-Optimization     | Design dependent           | 2x or more                                                                       |

## 1.1.1.1 Hyper-Retiming

Hyper-Retiming improves the performance of critical paths by moving registers out of the ALMs and into the interconnect. This technique balances register-to-register delays, and allows the design to run at a faster clock frequency. The Fitter automatically performs retiming optimizations to take advantage of the Hyper-Registers. However, you can enable further retiming optimizations by making the following types of changes to the RTL to remove retiming restrictions:

- Change the reset strategy to avoid using asynchronous clears

- Modifying timing constraints that prevent retiming

This process requires minimal effort, while resulting in an average performance gain of 1.4X for Stratix 10devices compared to previous generation high-performance FPGAs.

## 1.1.1.2 Hyper-Pipelining

Hyper-Pipelining eliminates long routing delays by adding additional pipeline stages in the interconnect between the ALMs. This technique allows the design to run at a faster clock frequency.

After you modify the RTL and place the prescribed number of pipeline stages at the boundaries of each clock domain, the Hyper-Retimer automatically places the registers within the clock domain at the optimal locations to maximize the performance. The combination of auto-placement and Fast-Forward Compile helps to automate the process when compared with conventional pipelining. This process requires minimal effort, while resulting in an average performance gain of 1.6X for devices compared to previous generation high-performance FPGAs.

## 1.1.1.3 Hyper-Optimization

After accelerating data paths through Hyper-Retiming and Hyper-Pipelining, some designs face limitations of control logic, such as long feedback loops and state machines. To achieve higher performance, restructure such logic sections to use functionally equivalent feed-forward or pre-compute paths, rather than long combinatorial feedback paths.

The effort that Hyper-Optimization requires varies by design characteristics. However, the technique can result in performance gains in Stratix 10 devices.

## 1.1.1.4 Fast Forward Compile

Fast Forward Compile guides you through the performance optimization and identifies performance limiting areas of the design. Fast Forward Compile analyzes the design and provides detailed recommendations about removing retiming restrictions, about how many pipeline stages should be added on critical paths, and how the design may be limited by bottlenecks such as feedback loops in the RTL. Fast Forward compile provides a summary of the estimated fmax improvement for each of the recommended changes. Use Fast Forward Compile to easily predict the highest performance of your Hyper-Optimized design in a Stratix 10 device.

## 1.1.1.5 Hyper-Aware Algorithms

The Quartus Prime Pro – Stratix 10 Edition Beta software includes Hyper-Aware algorithms used during synthesis and place-and-route. These algorithms allow the Compiler to reduce logic resources by predicting which registers can move out of ALMs and into Hyper-Registers in the interconnect routing.

The suite of HyperFlex architecture features, combines with the Intel 14-nm Tri-Gate process technology, to enable Stratix 10 FPGAs and SoCs that deliver the highest levels of performance, density, and power efficiency in programmable logic.

# 1.2 Acknowledgments

Examples in this document include code from the following OpenCores projects:

- 10\_100\_1000 Mbps tri-mode Ethernet MAC; by Jon Gao

- 128 bit AES Pipelined Cipher; by Amr Salah

- Turbo Decoder; by David Brochart

The projects are distributed under the LGPL license, and the terms are reproduced below.

Copyright (C) 2001, 2005 Authors

This source file may be used and distributed without restriction provided that this copyright statement is not removed from the file and that any derivative work contains the original copyright notice and the associated disclaimer.

This source file is free software; you can redistribute it and/or modify it under the terms of the GNU Lesser General Public License as published by the Free Software Foundation; either version 2.1 of the License, or (at your option) any later version.

This source is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the GNU Lesser General Public License for more details.

You should have received a copy of the GNU Lesser General Public License along with this source; if not, download it from http://www.opencores.org/lgpl.shtml

# **2 RTL Design Guidelines**

This section recommends specific design techniques to achieve the highest clock rates possible with the HyperFlex architecture and the Hyper-Retimer. Most common techniques of high-speed design apply to designing for the HyperFlex architecture. In addition, you must use some new techniques to achieve the highest performance.

Follow these general RTL design guidelines to enable the Hyper-Retimer to optimize design performance:

- Design in a way that facilitates register retiming by the Hyper-Retimer.

- Use a latency-insensitive design that supports the addition of pipeline stages at clock domain boundaries, top-level I/Os, and at the boundaries of functional blocks.

- Restructure RTL to avoid performance-limiting loops.

## 2.1 HyperFlex Design Philosophy

The Stratix 10 architecture represents a big step forward in maximum clock rate compared to previous FPGA generations. Migrating to the Stratix 10 architecture generally requires a review of design best practices to obtain the most benefit from Stratix 10 FPGAs. However, increasing the speed of your circuitry can produce dramatic effects.

## 2.1.1 Set a High-Speed Target

For silicon efficiency, set your speed target as high as possible. The Stratix 10 LUT is essentially a tiny ROM capable of a billion lookups per second. Operating a Stratix 10 LUT at 156 MHz uses only 15% of the capacity.

While setting a high-speed target, you must also maintain a comfortable guard band between the speed at which you can close timing, and the actual system speed required. Addressing the timing closure initially with margin is much easier.

## 2.1.1.1 Speed and Timing Closure

Timing closure difficulties occur when there is difference between what the circuit can naturally achieve, and the  $f_{MAX}$  requirement of your design. If the capability is sufficiently high, many possible placements are satisfactory, creating easy timing closure and short place-and-route runtime.

The timing in a slower circuit is not inherently easier to close than a faster one, because slow circuits tend to have large amounts of combinational logic between registers. When there are many nodes on a path, most possible placements involve

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

stretching nodes away from each other, resulting in significant routing delay. In contrast, a heavily pipelined circuit is much less dependent on placement, which makes closing timing easier, despite the higher speed.

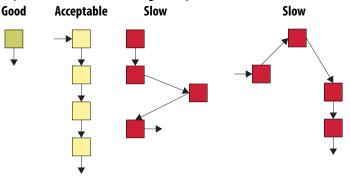

Figure 4. Placement of Deep or Under-Pipelined Paths

Examples of acceptable and slow routing delays.

Be realistic about timing margin when building your design. An Intel FPGA comprises a common pool of physical resources. Portions of the design make contact and distort one other as logic is added to the system. Adding stress to the system is typically detrimental to speed. As a design project progresses, there are more ways to slow the system down than to speed it up. Allowing more timing margin at the start helps mitigate this problem.

#### 2.1.1.2 Speed and Area or Latency

Running silicon at higher clock rates accomplishes more work with the same resources

The following table illustrates the rate of growth for various types of circuits as the bus width increases. The circuit functions interleave with big O notations of area as a function of bus width, starting at sub-linear with log(N), to super-linear with N\*N.

Table 2. Effect of Bus Width on Area

|               | Circuit Function |     |            |         |              |          |       |

|---------------|------------------|-----|------------|---------|--------------|----------|-------|

| Bus Width (N) | log N            | Mux | ripple add | N*log N | barrel shift | Crossbar | N*N   |

| 16            | 4                | 5   | 16         | 64      | 64           | 80       | 256   |

| 32            | 5                | 11  | 32         | 160     | 160          | 352      | 1024  |

| 64            | 6                | 21  | 64         | 384     | 384          | 1344     | 4096  |

| 128           | 7                | 43  | 128        | 896     | 896          | 5504     | 16384 |

| 256           | 8                | 85  | 256        | 2048    | 2048         | 21760    | 65536 |

Most circuit components use more than 2X the area as the bus width doubles. For a simple circuit like a mux, the area grows sub-linearly as the bus width increases. Cutting the bus width of a mux in half provides slightly worse linear area benefit. A ripple adder grows linearly as the bus width increases. More complex circuits, like barrel shifters and crossbars, grow super-linearly as bus width increases. If you cut the bus width of a barrel shifter, crossbar, or other complex circuit in half, the area benefit can be significantly better than half, approaching quadratic rates. For

components in which all inputs affect all outputs, increasing the bus width can cause quadratic growth. The expectation is then that, if you take advantage of speed-up to work on half-width buses, you generate a design with less than half the original area.

When working with streaming datapaths, the number of registers is a fair approximation of the latency of the pipeline in bits. Reducing the width by half creates the opportunity to double the number of pipeline stages without negatively impacting latency. Generally, the amount of additional registering required to go faster is significantly less than double, creating latency profit.

## 2.1.2 Experiment and Iterate

Experiment and iterate if your design's performance does not meet your requirements. The reprogrammability of Intel FPGAs allows you to experiment and optimize until you achieve your goals. Commonly, a design element's performance gradually becomes inadequate as requirements change over time. For example, when you apply the design element to a new context at a wider parameterization, perhaps the speed falls off.

When experimenting with circuit timing, there is no permanent risk from experimentation that temporarily breaks the circuit to collect a data point. A common trick of experienced designers is to add registers illegally to determine the effect on overall timing. If the candidate circuit begins to meet the timing objective, you can make further investment to legalize the change. If a circuit remains too slow, even when taking considerable liberties with registers, you likely must reconsider more basic elements of the design. Moving up or down a speed grade, or compressing circuitry in LogicLock Plus regions, are other helpful methods for speed investigation.

## 2.1.3 Compile Components Independently

Compile the design subcomponents as stand-alone entities to find the trouble spots. Competition for resources and physical constraints (like pin locations) tend to slow the overall design performance. Once embedded at a higher level, the block speed may be the same. However, the speed may never be any faster with other components than alone. As a margin of safety, establish a bright line rule for the required component speed. For example, when targeting a 20% timing margin, a component with 19.5% margin is a failure. You can base the targets on the context. For example, you can allow a timing margin of 10% for a high-level component representing half the chip. However, if the rule is not explicit, the margin erodes as 10% becomes 9%, then 6%, and so on.

Use the Chip Planner to visualize the system level view. The following floorplan shows a component that uses 5% of the logic on the device (central orange) and 25% of the M20K blocks (red stripes).

Figure 5. M20K Spread in Chip Planner

The system level view does not show anything alarming about the resource ratios. However, there is a great deal of mysterious routing congestion. The orange memory control logic fans out across a large physical span to connect to all of the memory blocks. The design functions satisfactorily alone, but struggles when unrelated logic cells fill up the intervening area. Restructuring this block to physically distribute the control logic better relieves the high-level problem.

Stand-alone compilation also prepares you for inevitable hardware debug cycles. Independent, coherent operation of portions of the design is beneficial. This condition allows test and modification of only those sections, without the runtime and complexities of the entire system.

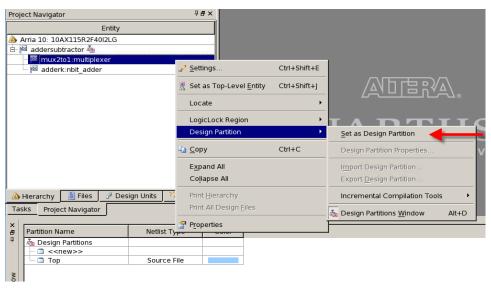

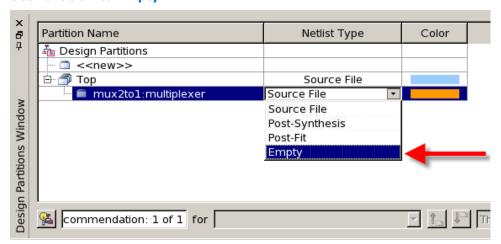

## 2.1.4 Optimize Sub-Modules

During design optimization, you can isolate the critical part in one or two sub-modules from a large design, and then compile the sub-modules. Compiling part of a design reduces compile time and allows you to focus on optimization of the critical part.

There are some caveats to this approach that you must be aware of to achieve the expected results for the entire design. Refer to the *Top-Level Considerations* section of the *HyperFlex Porting Guidelines* chapter for more information.

## **Related Links**

Top-Level Design Considerations on page 98

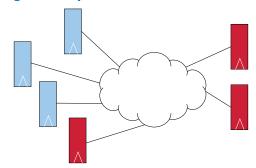

## 2.1.5 Avoid Broadcast Signals

Avoid using broadcast signals whenever possible. Broadcast signals are typically high fan-out control nets and can create large latency differences between paths. This latency difference increases the difficulty for the Hyper-Retimer to find a suitable location for registers, and can result in unbalanced delay paths. Use pipelining to address this issue and duplicate registers to drive broadcast signals.

Broadcast signals travel a large distance to reach individual registers. Because those fan-out registers may be spread out in the floorplan, use manual register duplication to improve placement. When choosing your register duplication technique, use placement knowledge to maximize benefits. The following figures show two examples in which the design uses extra registers to help close timing. However, the locations of the extra registers make the second example more efficient than the first.

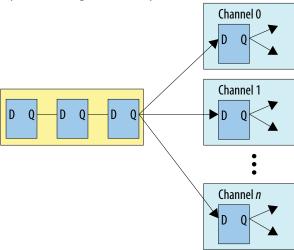

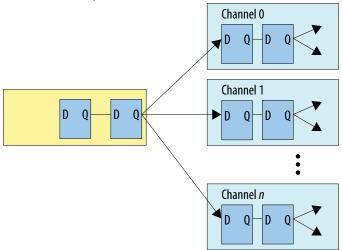

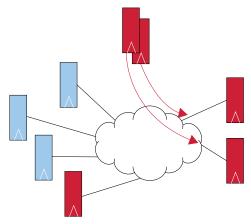

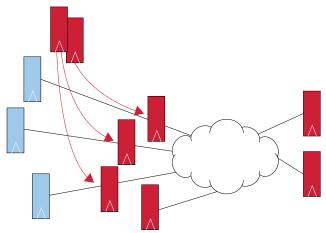

## Figure 6. Adding a Pipeline Stage to Broadcast Signals

The yellow box indicates extra registers in a module you add to help with timing. The block broadcasts the output to several transceiver channels. Because the final register stage fans out to destinations that cover a large physical area of the chip, these extra registers may not improve timing sufficiently.

#### Figure 7. A Better Approach to Pipelining Broadcast Signals

A better approach to pipelining is to duplicate the last pipeline register and place a copy of the register in the destination module (the transceiver channels in this example). This method results in better placement and better timing. The improvement occurs because each channel's pipeline register is placed to help cover the distance between the last register stage in the yellow module, and the registers in the transceivers, as needed. In addition to duplicating the last pipeline register, apply a dont\_merge synthesis attribute to avoid merging of the duplicate registers during synthesis, which eliminates any benefit.

The recommendation to manually duplicate some registers may seem to contradict one of the benefits of the HyperFlex architecture—that you no longer need to manually insert pipeline registers in optimal locations in the RTL. The Hyper-Retimer runs after placement and routing and optimizes  $f_{MAX}$  performance for the placed and routed design. In some cases, such as this example, there are still steps you can take manually to help the placer get a better result. The manual duplication in this example helps the placer get a better result, and that result is then further optimized by the Hyper-Retimer.

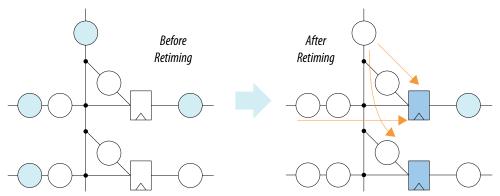

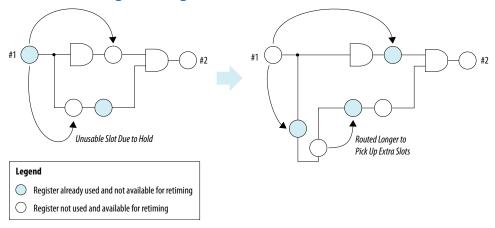

# 2.2 Facilitate Register Movement (Hyper-Retiming)

This section discusses facilitating register movement in your design (Hyper-Retiming). The Hyper-Retimer balances register chains to increase  $f_{MAX}$  by retiming some ALM registers into Hyper-Registers in the routing fabric. The *retiming* refers to moving the physical location of design registers to balance the propagation delay between registers. Retiming also performs sequential optimization by moving registers backwards and forwards across combinatorial logic. Retiming across node splits and merges may involve register duplications or merges. By balancing the propagation delays between each stage in a series of registers, the retiming process shortens the critical paths, reduces the clock period, and increases the frequency of operation.

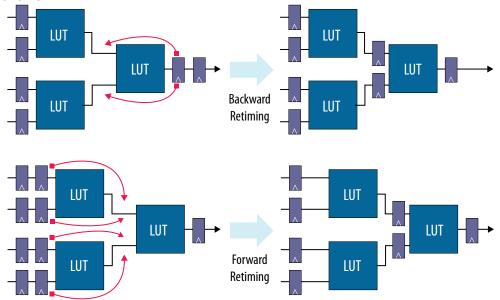

#### Figure 8. Moving Registers across LUTs

The left side represents the pre-retiming design, where the worst case delay is two LUTs. The right side represents the retiming design, which shows the worst case delay is one LUT.

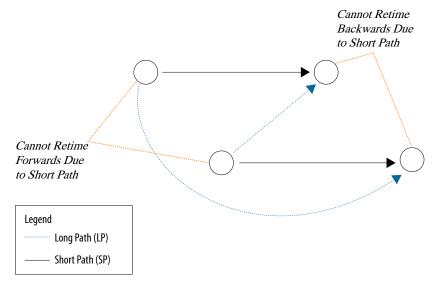

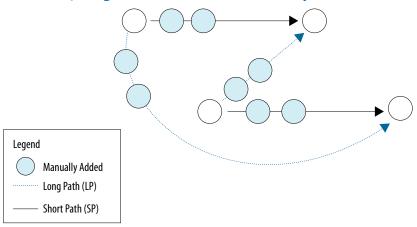

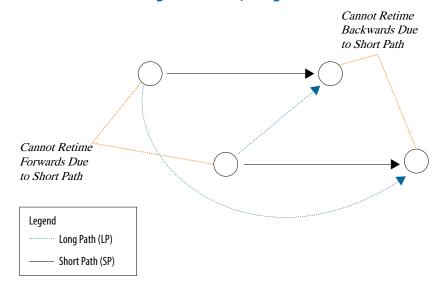

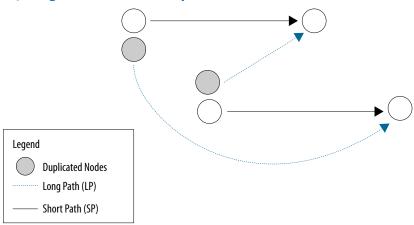

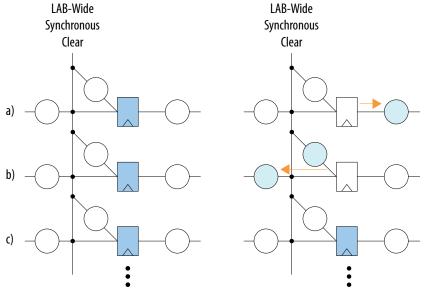

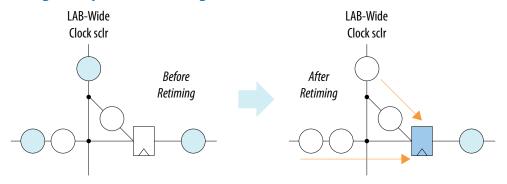

When the Hyper-Retimer cannot retime a register, this is known as a retiming restriction. Such restrictions limit the design's  $f_{MAX}$ . Minimize retiming restrictions in performance-critical parts of your designs to achieve the highest performance.

There are a variety of situations that limit performance. Some limitations relate to hardware characteristics, software behavior, or the design. Use the following design techniques to facilitate register retiming and avoid retiming restrictions:

- Avoid asynchronous resets, except where necessary. Refer to the Reset Strategies section.

- Avoid synchronous clears. Synchronous clears are usually broadcast signals that are not conducive to the retimer.

- Use targeted wildcards or names in timing constraints and exceptions. Refer to the *Timing Constraint Considerations* section.

- Avoid single cycle (stop/start) flow control. Examples are clock enables and FIFO full/empty signals. Consider using valid signals and almost full/empty, respectively.

- Avoid preserve or don't touch register attributes. Refer to the Retiming Restrictions and Workarounds section.

- For information about adding pipeline registers, refer to the *Add Pipeline Registers* (*Hyper-Pipelining*) section.

- For information about addressing loops and other RTL restrictions to retiming, refer to the *Optimize RTL (Hyper-Optimization)* section.

#### **Related Links**

Reset Strategies on page 16

This section recommends techniques to achieve maximum performance with resets.

- Timing Constraint Considerations on page 23

This section recommends specific timing constraint techniques to maximize performance.

- esc1445881977928.xml

- Add Pipeline Registers (Hyper-Pipelining) on page 26

This section discusses adding pipeline registers to increase performance.

- Retiming Restrictions and Workarounds on page 90

This section describes RTL design techniques you can use to avoid retiming restrictions.

## 2.2.1 Reset Strategies

This section recommends techniques to achieve maximum performance with resets. For the best performance, avoid resets (asynchronous and synchronous), except when necessary.

Because Hyper-Registers do not have asynchronous clears, you cannot retime any register with an asynchronous clear to improve performance.

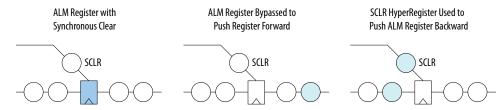

Using a synchronous clear instead of an asynchronous clear allows the Hyper-Retimer to retime the register. Refer to the *Synchronous Resets and Limitations* section for more detailed information about retiming behavior for registers with synchronous clears. Some registers in your design require synchronous or asynchronous clears, but you must minimize the number for best performance.

#### **Related Links**

Synchronous Resets and Limitations on page 119

#### 2.2.1.1 Removing Asynchronous Clears

You can remove asynchronous clears if a circuit naturally resets when the reset is held long enough to reach a steady-state equivalent of a full reset.

The following figure shows Verilog HDL and VHDL examples of common circuits that implement asynchronous clears for the registers in a processing pipeline.

Figure 10. Verilog HDL and VHDL RTL Examples with Asynchronous Clears

#### Verilog HDL always @(posedge clk, aclr) PROCESS(clk, aclr) BEGIN if (aclr) begin IF (aclr = '1') THEN reset\_synch <= '0'; reset\_synch <= 1'b0; aclr\_int <= 1'b0;</pre> aclr\_int <= '0'; end ELSIF rising\_edge(clk) THEN else begin reset\_synch <= '1';</pre> reset\_synch <= 1'b1;</pre> aclr\_int <= reset\_synch;</pre> aclr\_int <= reset\_synch;</pre> END IF; END PROCESS; end always @(posedge clk, aclr\_int) PROCESS(clk, aclr\_int) BEGIN if (aclr\_int) begin IF (aclr\_int = '1') THEN a <= 1'b0; a <= '0'; b <= 1'b0; b <= '0'; c <= '0'; c <= 1'b0; d <= 1'b0; d <= '0'; out <= 1'b0; output <= '0'; end ELSIF rising\_edge(clk) THEN else begin a <= input; a <= in; b <= a; b <= a; c <= b; c <= b; d <= c; d <= c; output <= d; out <= d; END IF; END PROCESS; end

Asynchronous clear clears all registers in the pipeline. They cannot be placed in Hyper-Registers.

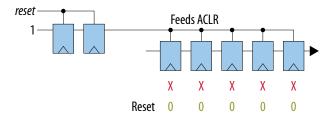

The following figure shows the same circuitry in schematic form, and shows the output behavior at reset.

Figure 11. Circuit Using Full Asynchronous Reset

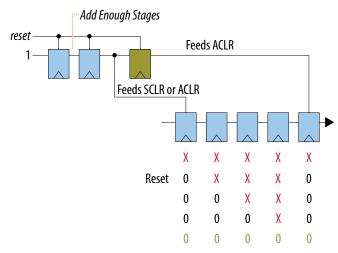

The following figure shows the removal of some of the asynchronous clears from the middle of the circuit. After a partial reset, if the modified circuit settles to the same steady state as the original circuit, then the modification is functionally equivalent.

Figure 12. Circuit Using Partial Asynchronous Reset

Cases involving inverting logic generally require additional synchronous clears to remain in the pipeline.

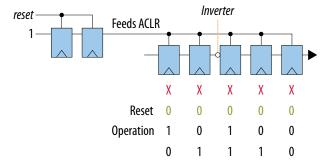

Figure 13. Circuit with an Inverter in the Register Chain

After removing the reset and applying the clock, the register outputs do not settle to the reset state, as in the circuit above. Rather, the inverting register cannot have its asynchronous clear removed to be equivalent to the above circuit after settling out of reset.

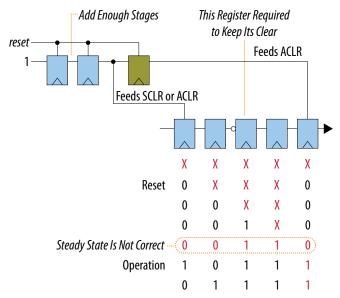

Figure 14. Circuit with an Inverter in the Register Chain with Asynchronous Clear

To avoid non-naturally resetting logic because of inverting functions, validate the output to synchronize with reset removal. Then, as long as the validating pipeline can enable the output when the computational pipeline is actually valid, the behavior is equivalent with reset removal. This process is suitable even if the computation portion of the circuit does not naturally reset.

Figure 15. Validating the Output to Synchronize with Reset

The next two figures show Verilog HDL and VHDL examples of the circuit shown in Figure 12 on page 18. You can apply this example to your design and remove unnecessary asynchronous resets.

#### Figure 16. **Verilog HDL Example Using Minimal or No Asynchronous Clears**

#### **Verilog HDL**

```

always @(posedge clk, posedge aclr)

if (aclr) begin

reset_synch_1 <= 1'b0;</pre>

reset_synch_2 <= 1'b0;</pre>

aclr_int <= 1'b0;</pre>

end

else begin

reset_synch_1 <= 1'b1;</pre>

reset_synch_2 <= reset_synch_1;</pre>

aclr_int <= reset_synch_2;</pre>

end

always @(posedge clk, posedge aclr_int)

if (aclr_int)

out <= 1'b0;

Asynchronous clear for

else

output register only

out <= d;

always @(posedge clk)

if (reset_synch_2)

a <= 1'b0;

Synchronous clear for

else

input register only

a <= in;

always @(posedge clk) begin

b <= a;

Naturally resetting registers

c <= b;

d <= c;

end

```

Synchronous clear for

Figure 17. VHDL Example Using Minimal or No Asynchronous Clears

```

input register only

PROCESS (clk, aclr) BEGIN

PROCESS (clk) BEGIN

IF (aclr = '1') THEN

IF rising_edge(clk) THEN

reset_synch_1 <= '0';

IF (reset_synch_2 = '1') THEN

reset_synch_2 <= '0';</pre>

a <= '0';

aclr_int <= '0';

ELSE

ELSIF rising_edge(clk) THEN

a <= input;

reset_synch_1 <= '1';

END IF;

reset_synch_2 <= reset_synch_1;</pre>

END IF;

aclr_int <= reset_synch_2;</pre>

END PROCESS;

END IF;

END PROCESS;

PROCESS (clk) BEGIN

IF rising_edge(clk) THEN

PROCESS (clk, aclr_int) BEGIN

b <= a;

IF (aclr_int = '1') THEN

c \le bi

output <= '0';

d <= c;

ELSIF rising_edge(clk) THEN

END IF;

output <= d;

END PROCESS;

END IF;

END PROCESS;

Naturally resetting registers

Asynchronous clear for

output register only

```

## 2.2.1.2 Synchronous Clears on Global Clock Trees

Using a global clock tree to distribute a synchronous clear may limit the Hyper-Retimer's performance improvements. Global clock trees do not have Hyper-Registers. As such, there is less flexibility to retime registers that fan out through a global clock tree compared to the routing fabric.

#### 2.2.1.3 Synchronous Resets on I/O Ports

The Hyper-Retimer does not retime registers driving an output port or being driven by an input port. If a synchronous clear is on one of these I/O registers, you cannot retime the register. This restriction is not typical of practical designs in which logic drives resets. However, this issue may become apparent in benchmarking a smaller piece of logic, where the reset may come from an I/O port. In this case, you cannot retime any of the registers that the reset drives. Adding some registers to the synchronous reset path corrects this condition.

#### 2.2.1.4 Duplicate and Pipeline Synchronous Resets

If a synchronous clear signal causes timing issues, duplicating the synchronous clear signal between the source and destination registers can resolve the timing issue. The registers pushed forward need not contend for Hyper-Register locations with registers being pushed back. For small logic blocks of a design, this method is a valid strategy to improve timing.

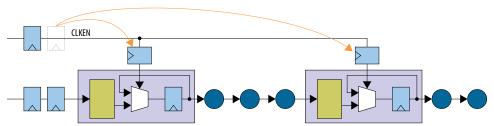

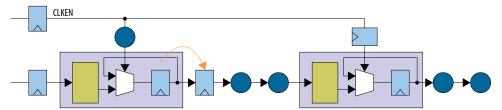

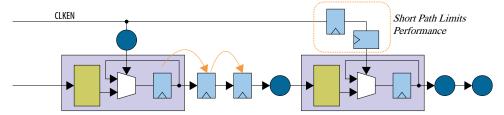

## 2.2.2 Clock Enable Strategies

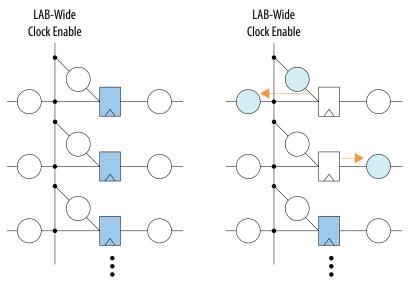

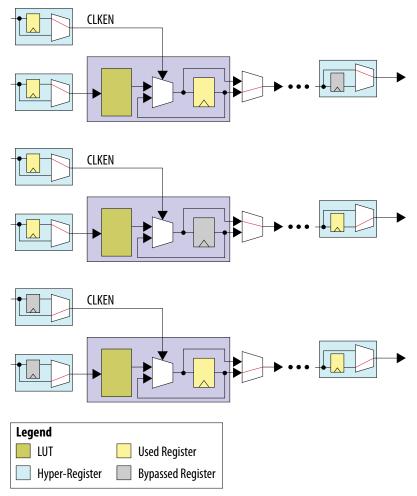

High fan-out clock enable signals can limit the performance achievable by the Hyper-Retimer. This section provides recommendations for three situations where you can use clock enables.

#### 2.2.2.1 Localized Clock Enable

The localized clock enable has a small fan-out. The localized clock enable often occurs in a clocked process or an always block, where the signal's behavior is undefined under a particular branch of a conditional case or if statement. As a result, the signal retains its previous value, which is a clock enable. To check whether a design has clock enables, view the **Fitter Report** ➤ **Plan Stage Section** ➤ **Control Signals** Compilation report and check the **Usage** column. Because the localized clock enable has a small fan-out, retiming it is quite easy and usually does not cause any timing issues.

## 2.2.2.2 High Fan-Out Clock Enable

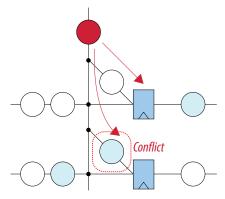

Avoid a high fan-out signal whenever possible. The high fan-out clock enable feeds a large amount of logic. The amount of logic is so large that the registers that you retime are pushing or pulling registers up and down the clock enable path for their specific needs. This pushing and pulling can result in conflicts along the clock enable line. This condition is similar to the aggressive retiming in the *Synchronous Resets Summary* section. Some of the methods discussed in that section, like duplicating the enable logic, are also beneficial in resolving conflicts along the clock enable line.

You typically use these high fan-out signals to disable a large amount of logic from running. These signals might occur when a FIFO's full flag goes high. You can often design around these signals. For example, you can design the FIFO to specify almost full a few clock cycles earlier, and allow the clock enable a few clock cycles to propagate back to the logic it disables. You can retime these extra registers into the logic if necessary.

#### **Related Links**

Synchronous Resets Summary on page 121

#### 2.2.2.3 Clock Enable with Timing Exceptions

Another consideration is for clock enable logic accompanied by multicycle and false path (occasionally) timing constraints. Clock enables are sometimes used to create a sub-domain that runs at half or quarter the rate of the main clock. Sometimes these clock enables control a single path with logic that changes every other cycle. However, the Hyper-Retimer does not retime registers that are endpoints of these timing exceptions. Because you typically use timing exceptions to relax timing, this case is less of an issue. If a clock enable validates a long and slow data path, and the path still has trouble meeting timing, consider adding a register stage to the data path. Also consider removing the multicycle timing constraint on the path. The Hyper-Aware CAD flow allows the retimer to retime the path to improve timing.

## 2.2.3 Synthesis Attributes

Your design may include registers with synthesis attributes such as preserve or dont\_touch. The Hyper-Retimer does not retime registers with preserve or dont\_touch attributes, because it respects the directive to prevent optimization. Consider whether you can remove the directives and allow the Hyper-Retimer to retime affected registers. If you preserve a register for debugging observability, consider keeping the preserve attribute. If you preserve a register to manage register duplication, consider using dont\_merge instead.

If you use the maxfan synthesis attribute, there is a side effect of applying a preserve attribute to the duplicated registers, which prevents the Hyper-Retimer from retiming the registers. You can remove the maxfan attribute and evaluate the performance without the attribute. Alternatively, you can remove the attribute and specify the Maximum Fan-Out assignment in the Quartus Settings File (.qsf), which does not have the side effect.

## 2.2.4 Timing Constraint Considerations

This section recommends specific timing constraint techniques to maximize performance.

Synopsys Design Constraints (.sdc) and exceptions, such as false paths and multicycle paths, restrict the retiming optimizations of the Hyper-Retimer. The Hyper-Retimer does not retime registers that are the endpoints of an SDC constraint. Define any constraints or exceptions as specific as possible to avoid Hyper-Retimer restrictions.

#### 2.2.4.1 Design Considerations for Multicycle Paths

This section describes special considerations for designs that include logic with multicycle exceptions. For example, your design may contain complex combinational logic that takes more than one clock cycle to process data. Some CRCs and arithmetic functions may include multicycle timing paths. You can reuse these modules and constraints unchanged in designs targeting Stratix 10 devices. However, the Hyper-Retimer does not retime registers that are endpoints of timing exceptions. Therefore, using actual register stages and removing the multicycle exception allows the Hyper-Retimer the most flexibility to improve performance.

For example, if you set up combinational logic with a multicycle exception of 3, you can remove the multicycle exception and insert two extra register stages before or after the combinational logic. This change allows the Hyper-Retimer to balance the extra register stages optimally through the logic.

## 2.2.4.2 Overconstraints

One timing closure technique is to add overconstraints to make the Fitter work harder on certain parts of a design. You may inadvertently limit the performance improvement if you use register-to-register overconstraints, because the Hyper-Retimer does retime registers that are the endpoints of an SDC constraint or exceptions. Overconstraints may be appropriate in some situations to improve performance. If you use overconstraints, do so sparingly as they may limit the achievable performance of the Hyper-Retimer. You may achieve higher performance without the overconstraint.

## 2.2.5 Clock Synchronization Strategies

Use a simple synchronization strategy to reach maximum speeds in the Stratix 10 architecture. Adding latency on paths with simple synchronizer crossings is straightforward. However, adding latency on other crossings is more complex.

The following figure shows a straightforward synchronization scheme in which the path goes from one register of the first domain (blue), directly to a register of the next domain (red).

Figure 18. Simple Clock Domain Crossing

To add latency in the red domain for retiming, add registers as shown.

Figure 19. Simple Clock Domain Crossing After Adding Latency

The following figure shows a domain crossing structure that is not recommended for use in Stratix 10 designs, but may exist in designs that target other device families:

- The design contains some combinational logic between the blue clock domain and the red clock domain. This logic is not properly synchronized and you cannot add registers flexibly.

- The blue clock domain drives the combinational logic and the logic contains paths that are launched on the red domain.

Figure 20. Clock Domain Crossing at Multiple Locations

In this case, you can add latency at the boundary of the red clock domain as shown in the figure below, as long as you do not add registers on a red to red domain path. Otherwise, the paths become unbalanced, potentially breaking the design functionality. Although technically possible, it is risky to add latency in this scenario. Before doing so, thoroughly analyze the various paths.

Figure 21. Clock Domain Crossing at Multiple Locations After Adding Latency

For Stratix 10 designs, synchronize the clock crossing paths before entering combinational logic. Adding latency is then more simple compared to the previous example.

In the following figure, the blue domain registers are synchronized to the red domain before entering the combinational logic. This design allows you to safely add extra pipeline registers in front of synchronizing registers without risking touching a red-red path inadvertently. This approach is the recommended synchronization method to take maximum advantage of the Stratix 10 architecture performance.

## Figure 22. Improved Clock Domain Synchronization

Recommended synchronization method to take maximum advantage of the Stratix 10 architecture.

## 2.2.6 Synchronizers

The Quartus Prime compilation flow detects registers that are part of a synchronizer chain. The Fitter tries to optimize those registers to increase the mean time between failure (MTBF) for Metastability. The Hyper-Retimer does not retime the registers detected as part of a synchronizer chain. Therefore, to provide more flexibility for retiming, consider adding more pipeline registers at clock domain boundaries.

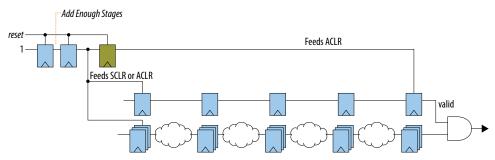

## 2.3 Add Pipeline Registers (Hyper-Pipelining)

This section discusses adding pipeline registers to increase performance. A proven way to increase  $f_{MAX}$  is to have a lot of registers and evenly distribute them throughout the circuit. At the high performance limit, a circuit has only one level of combinational logic between registers. If the register-to-combinational logic ratio is sufficient, the retimer can balance the registers to produce a design that is close to this ideal circuit.

Use Fast Forward Compilation during the design cycle to identify circuit boundaries that benefit from additional pipeline stages. Adding registers is much easier if you plan ahead to accommodate additional latency in your design. For more information about Fast Forward Compile, refer to the *Using Fast Forward Compilation* section.

At the most basic level, planning for additional latency means using parameterizable pipelines at the inputs and outputs of the clock domains in your design. For example, if Fast Forward Compile recommends adding two pipeline stages at an input bus, you can adjust a parameter and recompile. Refer to the *Appendix: Pipelining Examples* section for pre-written parameterizable pipeline modules in Verilog HDL, VHDL, and SystemVerilog.

Changing latency is more complicated than just adding pipeline stages. You might have to rework control logic, and other parts of the design or system software, to work properly with data arriving later. Making such changes could be difficult in existing RTL, but it may be easier in new parts of a design. Rather than hard-coding block latencies into control logic, try to make some of them parameters. In some types of systems, you may be able to add a "valid data" flag to pipeline stages in a processing pipeline and use that to trigger various computations, instead of relying on a high-level fixed concept of when data is valid.

Additional latency may also require changes to testbenches. When you create testbenches, use the same techniques you use to create latency-insensitive designs. Do not rely on a result becoming available in a predefined number of clock cycles, but consider checking a "valid data" or "valid result" flag.

Latency-insensitive design is not appropriate for every part of a system. Interface protocols that specify a number of clock cycles for data to become ready or valid must conform to those requirements and may not be able to accommodate changes in latency.

#### **Related Links**

- Using Fast Forward Compilation on page 65

This section describes using Fast Forward Compilation to guide you through the performance optimization process.

- Appendix: Parameterizable Pipeline Modules on page 50

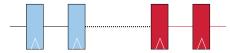

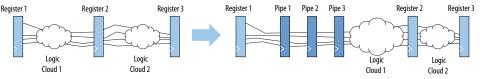

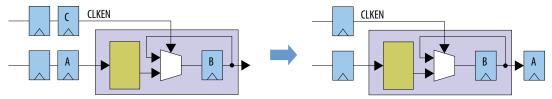

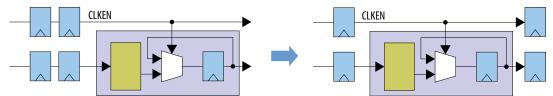

### 2.3.1 Conventional versus Hyper-Pipelining

This section describes how Hyper-Pipelining simplifies this process of conventional pipelining.

Conventional pipelining applies the following design modifications:

- Add two registers between logic clouds

- Modify HDL to insert a third register (or pipeline stage) into the design's logic cloud, which is Logic Cloud 2. This register insertion effectively creates Logic Cloud 2a and Logic Cloud 2b in the HDL

Figure 23. Conventional Pipelining User Modifications

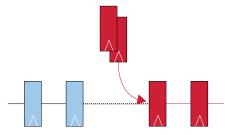

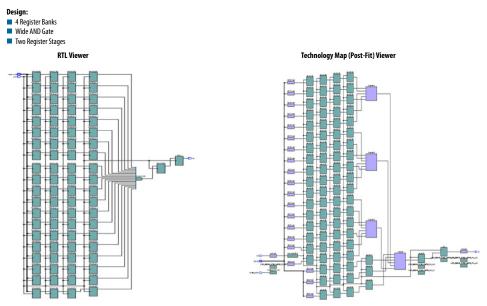

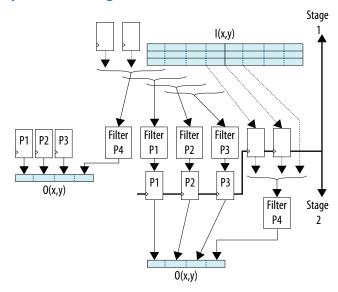

Hyper-Pipelining simplifies this process of adding registers. For the same design illustrated in the above figure, you add the registers—Pipe 1, Pipe 2, and Pipe 3—in aggregate at one location in the design RTL. Then, during design compilation, the Hyper-Retimer retimes the registers throughout the circuit to find the optimal placement along the path, as shown in the following figure. This optimization reduces path delay and maximizes the design's operating frequency.

## Figure 24. Hyper-Pipelining User Modifications

The following figure shows implementation of additional registers after the Hyper-Retimer compilation stage has completes optimization of the design.

Figure 25. Hyper-Pipelining and Hyper-Retimer Implementation

The resulting implementation in the Hyper-Pipelining flow differs from the conventional pipelining flow by the location of the Pipe 3 register. Because the Hyper-Retimer is aware of the current circuit implementation, including routing, it can more effectively locate the added aggregate registers to meet the design's maximum operating frequency. As shown in this example, Hyper-Pipelining requires significantly less effort than conventional pipelining techniques because you can place registers at a convenient location in a data path, and the compiler optimizes the register placements automatically.

## 2.3.2 Pipelining and Latency

Adding pipeline registers in a design increases the number of clock cycles necessary for a signal value to propagate through the design. Increasing the clock frequency can offset the increased latency.

Consider a design for a previous generation FPGA, with a 275 MHz  $f_{MAX}$  requirement. In the following figure, the path on the left achieves 286 MHz, limited by the 3.5 ns delay. Data takes three cycles to propagate through the register pipeline. Three cycles at 275 MHz is 10.909 ns to propagate through the pipeline.

Figure 26. Hyper-Pipeline Reduced Latency

Assume that the design is being retargeted to a Stratix 10 device, and the  $f_{MAX}$  requirement has doubled to 550 MHz. The path on the right in the above figure shows an additional pipeline stage that has been added and retimed, and the path now achieves 555 MHz, limited by the 1.8 ns delay. The data takes four cycles to propagate through the register pipeline. Four cycles at 550 MHz is 7.273 ns to propagate through the pipeline.

If your goal is to maintain the time to propagate through the pipeline with four stages compared to three, you could meet the 10.909 ns delay of the first version by increasing the  $f_{MAX}$  of the second version to 367 MHz, a 33% increase from 275 MHz.

## 2.3.3 Use Registers Instead of Multicycle Exceptions

Sometimes designs contain modules with complex combinational logic (such as CRCs and other arithmetic functions) that can take more than one clock cycle to process. These modules are constrained with multicycle exceptions, to relax the timing requirements through the block. You can reuse these modules and constraints unchanged in designs targeting Stratix 10 devices. Refer to the *Design Considerations for Multicycle Paths* section for more information.

You can insert a number of register stages in one convenient place in a module, and the Hyper-Retimer balances them automatically for you. For example, if you have a CRC function to pipeline, you do not need to identify the optimal decomposition and intermediate terms to register. Add the registers at its input or output, and the Hyper-Retimer can balance them.

#### **Related Links**

- Design Considerations for Multicycle Paths on page 23

This section describes special considerations for designs that include logic with multicycle exceptions.

- Appendix: Parameterizable Pipeline Modules on page 50

# 2.4 Optimize RTL (Hyper-Optimization)

This section describes multiple RTL restructuring techniques to improve performance.

## 2.4.1 Deciding When to Rewrite the RTL

Often you have an existing RTL design that requires optimization to meet a new performance target. How do you decide between modifying or completely rewriting the RTL? The Quartus Prime Fast Forward Compile feature helps you make the decision. For information about running Fast Forward Compile, refer to the *Using Fast Forward Compilation* section.

If even Fast Forward Compile performance is significantly below your target, consider redesigning parts of your circuit. If the Fast Forward Compile performance is above your target, it is feasible to achieve the target, although you may be unable to implement some of the recommendations required to achieve this performance.

When you decide to rewrite the RTL, plan an appropriate implementation. Because adding pipelining stages is a common Hyper-Optimization step, choose a design style that allows you to accommodate varying amounts of latency. Using parameters to define and express the latency of blocks can be an effective way to retain design flexibility.

For more suggestions, refer to the Experiment and Iterate section.

#### **Related Links**

- Using Fast Forward Compilation on page 65

This section describes using Fast Forward Compilation to guide you through the performance optimization process.

- Experiment and Iterate on page 11

Experiment and iterate if your design's performance does not meet your requirements.

## 2.4.2 General Optimization Techniques

Use the general RTL techniques this section describes to optimize the design for the HyperFlex architecture and the Hyper-Retimer.

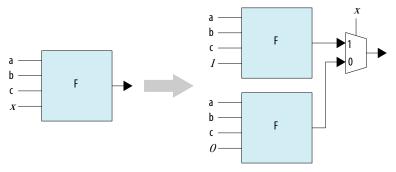

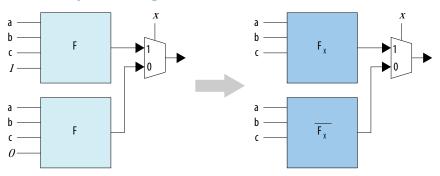

## 2.4.2.1 Shannon's Decomposition

Shannon's decomposition plays a role in Hyper-Optimization. Shannon's decomposition, or Shannon's expansion, is a way of factoring a Boolean function. You can express a function as  $F = x.F_x + x'F_x$ ' where  $x.F_x$  and  $x'F_x$ ' are the positive and negative co-factors of the function F with respect to x. You can factor a function with four inputs as, (a, b, c, x) = x.(a, b, c, 1) + x'.F(a, b, c, 0), as shown in the following diagram.

Figure 27. Shannon's Decomposition

Logic synthesis can take advantage of the constant-driven inputs and slightly reduce the cofactors, as shown in the following diagram.

Figure 28. Shannon's Decomposition Logic Reduction

In Hyper-Optimization, the advantage of Shannon's decomposition is that it pushes the x signal to the head of the cone of input logic, making the x signal the fastest path through the cone of logic. The x signal becomes the fastest path at the expense of all other signals. Using Shannon's decomposition also doubles the area cost of the original function.

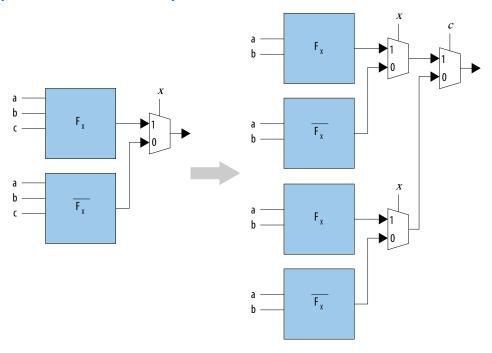

The following diagram shows how you can repeatedly use Shannon's decomposition to decompose functions with more than one critical input signal, thus increasing the area cost.

Figure 29. Repeated Shannon's Decomposition

Shannon's decomposition can be an effective optimization technique for loops. When you perform Shannon's decomposition on logic in a loop, the logic in the loop moves outside the loop. The Hyper-Retimer can now pipeline the logic moved outside the loop.

The following diagram shows a loop that contains a single register, four levels of combinational logic, and an additional input. Adding registers in the loop changes the functionality, but you can move the combinational logic outside the loop by performing Shannon's decomposition.

Figure 30. Loop Example before Shannon's Decomposition

The output of the register in the loop is 0 or 1. You can duplicate the combinational logic that feeds the register in the loop, tying one copy's input to 0 and the other copy's input to 1. The register in the loop then selects one of the two copies, as shown in the following diagram.

Figure 31. Loop Example after Shannon's Decomposition

Performing Shannon's decomposition on the logic in the loop reduces the amount of logic in the loop. The Hyper-Retimer can now perform Hyper-Retiming or Hyper-Pipelining on the logic removed from the loop, and increase the circuit performance.

## 2.4.2.1.1 Shannon's Decomposition Example

The sample circuit adds or subtracts an input value from the internal\_total value based on its relationship to a target value. The core of the circuit is the target\_loop module, shown in the following example.

## **Example 1. Source Code before Shannon's Decomposition**

```

module target_loop (clk, sclr, data, target, running_total);

parameter WIDTH = 32;

input clk;

input sclr;

input [WIDTH-1:0] data;

input [WIDTH-1:0] target;

output [WIDTH-1:0] running_total;

reg [WIDTH-1:0] internal_total;

always @(posedge clk) begin

if (sclr)

begin

internal_total <= 0;</pre>

else begin

internal_total <= internal_total + ((( internal_total > target) ? -

data:data)* target/4));

end

assign running_total = internal_total;

end module

```

The module uses a synchronous clear, based on the recommendations to enable Hyper-Retiming.

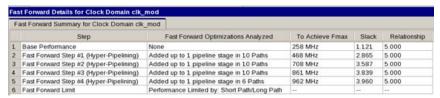

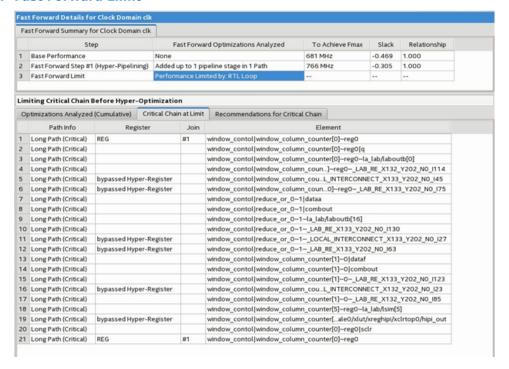

The following figure shows the Fast Forward Compile report for the target\_loop module instantiated in a register ring.

Figure 32. Fast Forward Compile Report before Shannon's Decomposition

| F | Fast Forward Summary for Clock Domain clk |                                    |                 |        |             |                      |  |  |  |

|---|-------------------------------------------|------------------------------------|-----------------|--------|-------------|----------------------|--|--|--|

|   | Step                                      | Fast Forward Optimizations Applied | To Achieve Fmax | Slack  | Requirement | Limiting Reason      |  |  |  |

| 1 | Base Performance                          | 0, including 0 pipeline stages     | 247.1 MHz       | -3.047 | 0.970       | Short Path/Long Path |  |  |  |

| 2 | Fast Forward Step #1                      | 29, including 1 pipeline stage     | 248.94 MHz      | -3.017 | 0.970       | Loop                 |  |  |  |

| 3 | Hyper-Optimization                        | 29, including 1 pipeline stage     |                 |        | 0.970       | Loop                 |  |  |  |

The Hyper-Retimer achieves about 248 MHz by adding a pipeline stage in the Fast Forward Compile. The Limiting Reason column indicates that the critical chain is a loop. Examining the critical chain report reveals that there is a repeated structure in the chain segments. The repeated structure is shown as an example in the *Optimizing Loops* section.

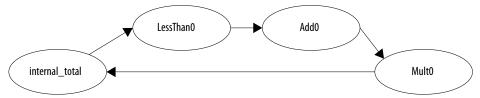

The following diagram shows a structure that implements the expression in the previous example code. The functional blocks correspond to the comparison, addition, and multiplication operations. The zero in each arithmetic block's name is part of the synthesized name in the netlist. The zero is because the blocks are the first zero-indexed instance of those operators created by synthesis.

#### Figure 33. Elements of a Critical Chain Sub-Loop

This expression is a candidate for Shannon's decomposition. Instead of performing only one addition with the positive or negative value of data, you can perform the following two calculations simultaneously:

- internal\_total (data \* target/4)

- internal\_total + (data \* target/4)

You can then use the result of the comparison internal\_total > target to select which calculation result to use. The modified version of the code that uses Shannon's decomposition to implement the internal\_total calculation is shown in the following example.

#### **Example 2. Source Code after Shannon's Decomposition**

```

module target_loop_shannon (clk, sclr, data, target, running_total);

parameter WIDTH = 32;

input clk;

input sclr;

input [WIDTH-1:0] data;

input [WIDTH-1:0] target;

output [WIDTH-1:0] running_total;

reg [WIDTH-1:0] internal_total;

wire [WIDTH-1:0] total_minus;

wire [WIDTH-1:0] total_plus;

assign total_minus = internal_total - (data * (target / 4));

assign total_plus = internal_total + (data * (target / 4));

always @(posedge clk) begin

```

```

if (sclr)

begin

internal_total <= 0;

end

else begin

internal_total <= (internal_total > target) ? total_minus:total_plus);

end

end

assign running_total = internal_total;

endmodule

```

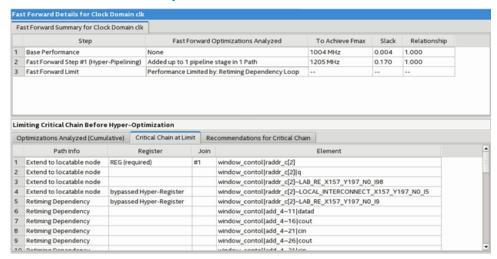

As shown in the following figure, the performance almost doubles after recompiling the design with the code change.

#### Figure 34. Fast Forward Compile Report after Shannon's Decomposition

| F           | ast Forward Summary fo | r Clock Domain clk                 |                 |        |             |                        |

|-------------|------------------------|------------------------------------|-----------------|--------|-------------|------------------------|

|             | Step                   | Fast Forward Optimizations Applied | To Achieve Fmax | Slack  | Requirement | Limiting Reason        |

| 1           | Base Performance       | 0, including 0 pipeline stages     | 486.85 MHz      | -1.054 | 0.970       | Insufficient Registers |

| 2           | Fast Forward Step #1   | 37, including 1 pipeline stage     | 495.79 MHz      | -1.017 | 0.970       | Short Path/Long Path   |

| 1<br>2<br>3 | Hyper-Optimization     | 37, including 1 pipeline stage     |                 |        | 0.970       | Short Path/Long Path   |

#### 2.4.2.1.2 Identifying Circuits for Shannon's Decomposition

The circuits in which you can rearrange many inputs to control the final select stage are good candidates for Shannon's decomposition. Be aware of the new logic depths while restructuring logic to use a subset of the inputs to control the select stage. Ideally, the logic depth to the select signal is similar to the logic depth to the selector inputs. Practically, there is a difference in the logic depths because it is difficult to perfectly balance the number of inputs feeding each cloud of logic.

Another candidate for Shannon's decomposition is a circuit with only one or two signals in the cone of logic that are truly critical, and others are static, or with clearly lower priority.

Shannon's decomposition can incur a significant area cost, especially if the function is complex. There are other optimization techniques that have a lower area cost, as described in this document.

### 2.4.2.2 Time Domain Multiplexing

Time domain multiplexing increases circuit throughput by using multiple threads of computation. This technique is also known as C-slow retiming, or multithreading.

This technique replaces each register in a circuit by a set of C registers in series. Each extra copy of registers creates a new computation thread. One computation through the modified design takes C times as many clock cycles as the original circuit. However, the Hyper-Retimer can retime the additional registers to improve the  $f_{MAX}$  by a factor of C. For example, instead of instantiating two modules running at 400 MHz, you can instantiate one module running at 800 MHz.

The following set of diagrams shows the process of C-slow retiming, beginning with an initial circuit.

#### Figure 35. C-slow Retiming Starting Point

You edit the RTL design to replace every register, including registers in loops, with a set of C registers, made up of one register per independent thread of computation. If you replaced each register with two registers, the circuit is as shown in the following figure.

### Figure 36. C-slow Retiming Intermediate Point

Compile the circuit at this point. When the Hyper-Retimer optimizes the circuit, it has more flexibility to perform Hyper-Retiming with the additional registers. The optimized circuit is as shown in the following figure.

#### Figure 37. C-Slow Retiming Ending Point

In addition to replacing every register with a set of registers, you must also multiplex the multiple input data streams into the block, and demultiplex the output streams out of the block.

#### 2.4.2.2.1 Identifying Time Domain Multiplexing Optimization Opportunities

Use time domain multiplexing when a design includes multiple parallel threads, each limited by a loop. The module being optimized must not be sensitive to latency.

## 2.4.2.3 Loop Unrolling

Loop unrolling moves logic out of the loops, and into feed-forward flows. You can further optimize the logic with additional pipeline stages.

#### 2.4.2.4 Precomputation

Precomputation is one of the easiest and most beneficial techniques for optimizing overall design speed. When confronted with critical logic, verify whether the signals the computation implies are available earlier. Always compute signals as early as possible to keep these computations outside of critical logic.

When trying to keep critical logic outside your loops, try precomputation first. The Compiler cannot optimize logic within a loop easily using retiming only. Registers inside the loop cannot be moved outside of it; registers outside the loop cannot be retimed into the loop. Therefore, keep the logic inside the loop as small as possible so that it does not negatively impact your  $f_{\text{MAX}}$ .

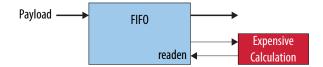

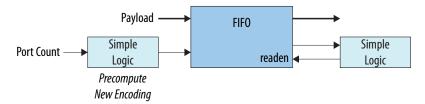

The following figure shows a FIFO block diagram before and after precomputation. The diagram before precomputation depicts a payload going through a FIFO to some computational logic. The computational logic then sends control signals back to the FIFO for processing. If the loop created by the FIFO and calculation logic is large and depends on multiple signals, instead precompute the results to minimize the calculation logic.

After precomputation, logic is minimized in the loop and the design precomputes the encodings. The calculation is outside of the loop, and you can optimize it with pipelining or retiming. You cannot remove the loop, but can better control the effect of the loop on the design speed.

Figure 38. Restructuring a Design with an Expensive Loop

## **Before Precomputation**

## **After Precomputation**

The following code example shows a similar problem. The original loop contains comparison operators.

```

StateJam:if

(RetryCnt <=MaxRetry&&JamCounter==16)

Next_state=StateBackOff;

else if (RetryCnt>MaxRetry)

Next_state=StateJamDrop;

else

Next_state=Current_state;

```

Precomputing the values of RetryCnt<=MaxRetry and JamCounter==16 removes the expensive computation from the StateJam loop and replaces it with simple boolean operations. The modified code is:

```

reg RetryCntGTMaxRetry;

reg JamCounterEqSixteen;

StateJam:if

(!RetryCntGTMaxRetry && JamCounterEqSixteen)

Next_state=StateBackOff;

else if (RetryCntGTMaxRetry)

Next_state=StateJamDrop;

Next_state=Current_state;

always @ (posedge Clk or posedge Reset)

if (Reset)

JamCounterEqSixteen <= 0;</pre>

else if (Current_state!=StateJam)

JamCounterEqSixteen <= 0;</pre>

JamCounterEqSixteen <= (JamCounter == 15) ? 1:0;</pre>

always @ (posedge Clk or posedge Reset)

if (Reset)

RetryCntGTMaxRetry <= 0;</pre>

else if (Current_state==StateSwitchNext)

```

```

RetryCntGTMaxRetry <= 0;

else if (Current_state==StateJam&&Next_state==StateBackOff)

RetryCntGTMaxRetry <= (RetryCnt >= MaxRetry) ? 1: 0;

```

# 2.4.3 Specific Design Structures

This section describes common performance bottleneck structures, and recommendations to improve  $f_{\text{MAX}}$  performance for each case.

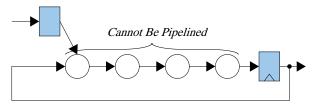

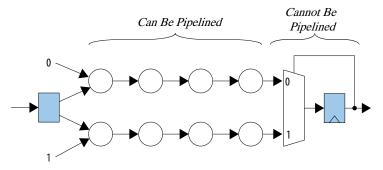

# 2.4.3.1 Restructuring Loops

Many restructuring techniques target loops, which fundamentally limit performance. A loop is a feedback path in a circuit. Loops may be simple and short, with a small amount of combinational logic on a feedback path. Loops may be much more complex, potentially going through multiple other registers on the way back to the original register. All useful circuits contain loops.

Loops limit performance because adding pipeline stages in a loop changes its functionality. The Hyper-Retimer never retimes registers into a loop. However, you can change RTL to restructure loops to improve performance. Perform loop optimizations after analyzing performance bottlenecks with Fast Forward Compile. You can also apply these techniques proactively as you write new RTL, to maximize performance potential. You can also use these techniques to improve performance in existing RTL, especially when you review performance bottlenecks in the Hyper-Retimer reports.

The following sections describe these techniques.

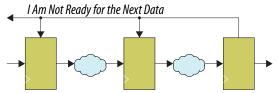

# 2.4.3.2 Control Signal Backpressure

This section describes RTL design techniques to control signal backpressure. The Stratix 10 architecture is extremely efficient at streaming data. Because the architecture supports very high clock rates, it is difficult to send feedback signals to reach large amounts of logic in one clock cycle. Inserting extra pipeline registers has the side effect of increasing backpressure on control signals. Data must flow forward as much as possible.

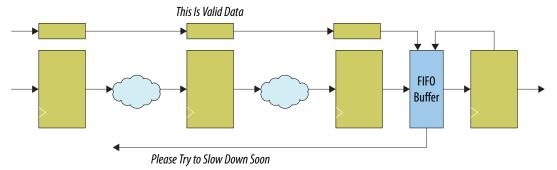

## Figure 39. Control Signal Backpressure

Single clock cycle control signals create loops that can prevent or reduce the effectiveness of pipelining and register retiming. This example depicts a ready signal that notifies the upstream register of readiness to consume data. The ready signals must freeze multiple data sources at the same time.

Modifying the original RTL to add a small FIFO buffer that relieves the pressure upstream is a straightforward process. When the logic downstream of this block is not ready to use the data, the FIFO stores the data.

Figure 40. Using a FIFO Buffer to Control Backpressure

The goal is for data to reach the FIFO buffer every clock cycle. An extra bit of information decides whether the data is valid and should be stored in the FIFO buffer. The critical signal now resides between the FIFO buffer and the downstream register that consumes the data. This loop is much smaller. You can now use pipelining and register retiming to optimize the section upstream of the FIFO buffer.

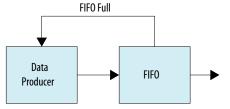

# 2.4.3.3 Flow Control with FIFO Status Signals

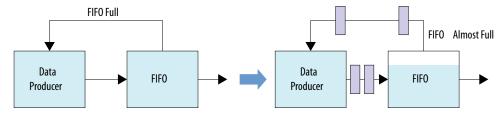

Because of the high clock speeds achievable by Stratix 10 devices, use extra care when dealing with flow control signals. This practice is particularly important with signals that gate a data path in multiple locations at the same time. For example, this practice is important with clock enable or FIFO full/empty signals. Instead of working with immediate control signals, use a delayed signal. Looking at the FIFO example, one can build a buffer within the FIFO block. The control signals indicate to the upstream data path that it is almost full, leaving a few clock cycles for the upstream data to receive their gating signal. This approach alleviates timing closure difficulties on the control signals.

When you use FIFO full and empty signals, you must process these signals in one clock cycle to prevent overflow or underflow.

# Figure 41. FIFO Flow Control Loop

The loop is formed while reading control signals from the FIFO.

If you use an almost full or almost empty signal instead, you can add pipeline registers in the flow control loop. The lower you make the almost full threshold, and the higher you make the almost empty threshold, the more registers you can add to the signal.

The following example has two extra registers in the full control flow signal. When the FIFO block signals that it is nearly full, the circuit requires two clock cycles to stop the data flow. Size the FIFO block to allow for proper storage of those extra valid data. The extra two pipeline registers in the control path help with routing, and enable higher speed than with traditional single-cycle FIFO control scheme.

Figure 42. Improved FIFO Flow Control Loop with Almost Full instead of Full FIFO

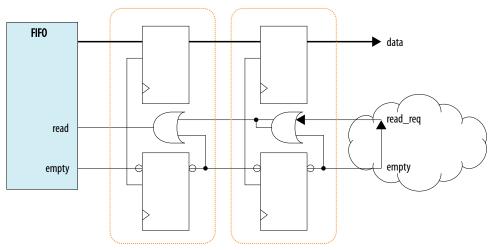

You can use skid buffers to pipeline a FIFO. If necessary, you can cascade skid buffers. When you insert skid buffers, they unroll the loop that includes the FIFO control signals. The skid buffers do not eliminate the loop in the flow control logic, but the loop transforms into a series of shorter loops. In general, switch to almost empty and almost full signals instead of using skid buffers.

Figure 43. FIFO Flow Control Loop with Two Skid Buffers in a Read Control Loop

If you have loops involving FIFO control signals, and they are broadcast to many destinations for flow control, you should carefully consider whether there is a way to eliminate the broadcast signals. Pipeline broadcast control signals, and use almost full and almost empty status bits from FIFOs.

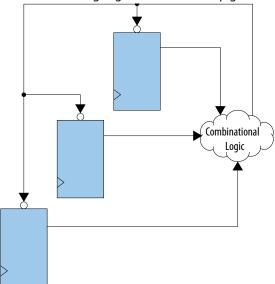

# 2.4.3.4 Read-Modify-Write Memory

Wireline networking applications often require updating counter values every clock cycle. This process is challenging because the number of queues and counters increases along with bandwidth requirements. If you pipeline a counter update over multiple clock cycles, maintain a cache to track recent activity with a particular counter. As you increase the number of cycles to update the value, the amount of logic required to handle caching and data combination increases, and can be difficult to scale. Loops are inherent in the logic for the cache, and they can be difficult to optimize.

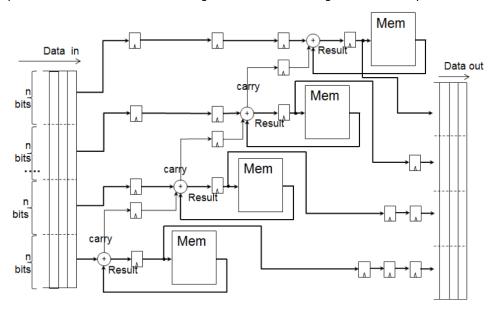

A technique to improve performance, without extra complexity, is to break the modification operation into smaller blocks that can be completed in one clock cycle.

# Figure 44. Pipelining Read-Modify-Write Memory

This figure shows a method to pipeline a read-modify-write memory to improve performance without maintaining a cache for tracking recent activity.

Data words are split into multiple n-bit chunks, where each chunk is small enough to be processed efficiently in one clock cycle. For the best performance, each chunk must be no wider than one M20K memory block.

A loop in a read-modify-write circuit is unavoidable because of the nature of the circuit, but the loop in this solution is small and short. This solution is scalable, because the underlying structure remains unchanged regardless of the number of pipeline stages. If you need higher  $f_{MAX}$ , increase the number of memory blocks, use narrower memory blocks, and increase the latency. If you need lower latency, use fewer, wider memory blocks, and remove pipeline stages appropriately.

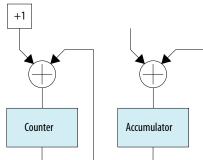

## 2.4.3.5 Counters and Accumulators

Performance-limiting loops occur rarely in small, simple counters. Counters with unnatural rollover conditions (not a power of two), or irregular increments, are more likely to have a performance-limiting critical chain. When a performance-limiting loop occurs in a small counter (roughly 8 bits or less), write the counter as a fully decoded state machine, depending on all the inputs that control the counter. The counter still contains loops, but they are smaller, and not performance-limiting. When the counter is small (roughly 8 bits or less), the fitter implements it in a single LAB. This implementation makes the counter fast because all the logic is placed close together.

You can also use loop unrolling to improve counter performance.

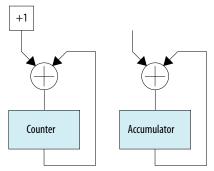

## Figure 45. Counter and Accumulator Loop

In a counter and accumulator loop, a register's new value depends on its old value. This includes variants like LFSRs (linear feedback shift register) and gray code counters.

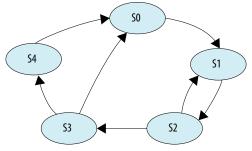

## 2.4.3.6 State Machines

Loops due to state machines can be difficult to optimize. Carefully examine the state machine logic to determine whether you can precompute any signals used in the next state logic.

To effectively pipeline the state machine loop, consider adding skips states to a state machine. Skips states are states added to allow more transition time between two adjacent states.

To optimize state machine loops, sometimes it may be necessary to write a new state machine.

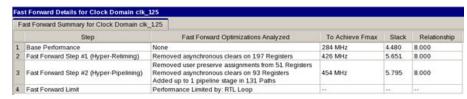

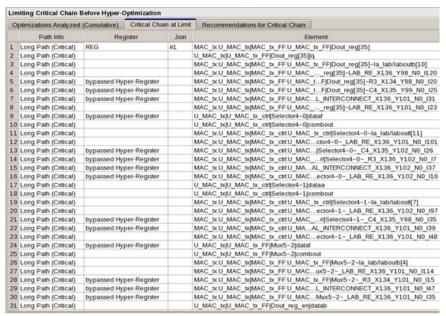

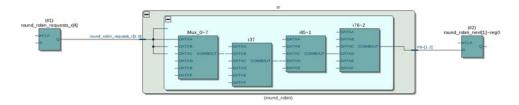

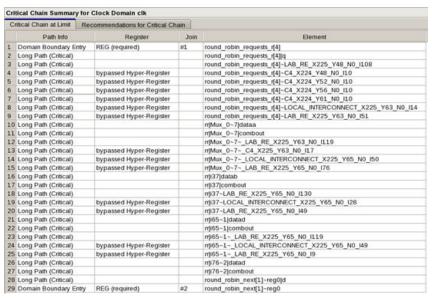

## Figure 46. State Machine Loop